$9.7400

$5.9500

$4.1400

$9.3100

$9.7400

$2.6100

$2.7400

$2.5200

$9.2100

$2.5200

$2.6300

$2.6300

$9.7400

$6.1400

$2.5200

$6.0400

$2.5200

$6.8600

$2.5800

$6.1400

$18.6100

$6.0400

$4.1000

$2.5200

$3.9500

$9.7400

$3.8400

$2.5200

$5.7600

$3.9500

$2.9300

$3.9200

$2.5800

$4.2600

$5.5700

$2.5800

$10.1200

$3.3500

$9.7400

$4.1000

Samsung eMCP UMCP

Part number

Capacity

Version

DRAM Capacity

DRAM

Package

Rate

Production

KM2F8001CM-B707

256GB

UFS2.1

48Gb

LPDDR4X

254FBGA

4266Mbps

MassProduction

KM2P8001CM-B518

64GB

UFS2.1

48Gb

LPDDR4X

254FBGA

4266Mbps

Sample

KM3P6001CM-B517

64GB

eMMC

48Gb

LPDDR4X

254FBGA

4266Mbps

Sample

KM5C7001DM-B622

64GB

UFS2.1

32Gb

LPDDR4X

254FBGA

4266Mbps

MassProduction

KM5H80018M-B424

64GB

UFS2.1

24Gb

LPDDR4X

254FBGA

4266Mbps

MassProduction

KM5P8001DM-B424

64GB

UFS2.1

32Gb

LPDDR4X

254FBGA

4266Mbps

Sample

KM8F8001JA-B813

256GB

UFS2.1

64Gb

LPDDR4X

254FBGA

4266Mbps

MassProduction

KM8F8001JM-B813

256GB

UFS2.1

64Gb

LPDDR4X

254FBGA

4266Mbps

MassProduction

KM4X6001KM-B321

32GB

eMMC5.1

16Gb

LPDDR4X

254FBGA

4266Mbps

MassProduction

KM8V8001JM-B813

128GB

UFS2.1

64Gb

LPDDR4X

254FBGA

4266Mbps

MassProduction

KMDP60018M-B425

64GB

eMMC5.1

24Gb

LPDDR4X

254FBGA

4266Mbps

MassProduction

KMFN60012B-B214

8GB

eMMC5.1

8Gb

LPDDR3

221FBGA

1866Mbps

MassProduction

KMGX6001BA-B514

32GB

eMMC5.1

24Gb

LPDDR3

221FBGA

1866Mbps

MassProduction

KMQE60013B-B318

16GB

eMMC5.1

16Gb

LPDDR3

221FBGA

1866Mbps

MassProduction

KM2V8001CM-B707

128GB

UFS2.1

48Gb

LPDDR4X

254FBGA

4266Mbps

MassProduction

KMGP6001BA-B514

32GB

eMMC5.1

16Gb

LPDDR3

221FBGA

1866Mbps

MassProduction

KMQX60013A-B419

32GB

eMMC5.1

16Gb

LPDDR3

221FBGA

1866Mbps

MassProduction

Samsung EMMC

Part number

Version

Capacity

VCC

接口

Package

Temperature

Production

KLMCG2UCTB-B041

eMMC5.1

64GB

1.8/3.3V

HS400

11.5x13x0.8mm

-25~85°C

MassProduction

KLMDG4UCTB-B041

eMMC5.1

128GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

MassProduction

KLM4G1FETE-B041

eMMC5.1

4GB

1.8,3.3V/3.3V

HS400

11x10x0.8mm

-25~85°C

MassProduction

KLM8G1GEUF-B04P

eMMC5.1

8GB

1.8/3.3V

HS400

11.5x13x0.8mm

-40~85°C

MassProduction

KLM8G1GEUF-B04Q

eMMC5.1

8GB

1.8/3.3V

HS400

11.5x13x0.8mm

-40~105°C

MassProduction

KLMAG2GEUF-B04P

eMMC5.1

16GB

1.8/3.3V

HS400

11.5x13x0.8mm

-40~85°C

MassProduction

KLMAG2GEUF-B04Q

eMMC5.1

16GB

1.8/3.3V

HS400

11.5x13x0.8mm

-40~105°C

MassProduction

KLMBG4GEUF-B04P

eMMC5.1

32GB

1.8/3.3V

HS400

11.5x13x0.8mm

-40~85°C

MassProduction

KLMBG4GEUF-B04Q

eMMC5.1

32GB

1.8/3.3V

HS400

11.5x13x0.8mm

-40~105°C

MassProduction

KLMCG2KCTA-B041

eMMC5.1

64GB

1.8/3.3V

HS400

11.5x13x0.8mm

-25~85°C

MassProduction

KLMCG2UCTA-B041

eMMC5.1

64GB

1.8/3.3V

HS400

11.5x13x0.8mm

-25~85°C

MassProduction

KLMDG4UCTA-B041

eMMC5.1

128GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

MassProduction

KLMEG8UCTA-B041

eMMC5.1

256GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

MassProduction

KLM8G1GEME-B041

eMMC5.1

8GB

1.8/3.3V

HS400

11.5x13x0.8mm

-25~85°C

EOL

KLM8G1GEND-B031

eMMC5.0

8GB

1.8/3.3V

HS400

11.5x13x0.8mm

-25~85°C

EOL

KLM8G1GESD-B03P

eMMC5.0

8GB

1.8/3.3V

HS400

11.5x13x0.8mm

-40~85°C

MassProduction

KLM8G1GESD-B03Q

eMMC5.0

8GB

1.8/3.3V

HS400

11.5x13x0.8mm

-40~105°C

MassProduction

KLM8G1GESD-B04P

eMMC5.1

8GB

1.8/3.3V

HS400

11.5x13x0.8mm

-40~85°C

MassProduction

KLM8G1GESD-B04Q

eMMC5.1

8GB

1.8/3.3V

HS400

11.5x13x0.8mm

-40~105°C

MassProduction

KLM8G1GETF-B041

eMMC5.1

8GB

1.8,3.3V/3.3V

HS400

11.5x13x0.8mm

-25~85°C

MassProduction

KLM8G1WEPD-B031

eMMC5.0

8GB

1.8/3.3V

HS400

11.5x13x0.8mm

-25~85°C

EOL

KLMAG1JENB-B041

eMMC5.1

16GB

1.8/3.3V

HS400

11.5x13x0.8mm

-25~85°C

EOL

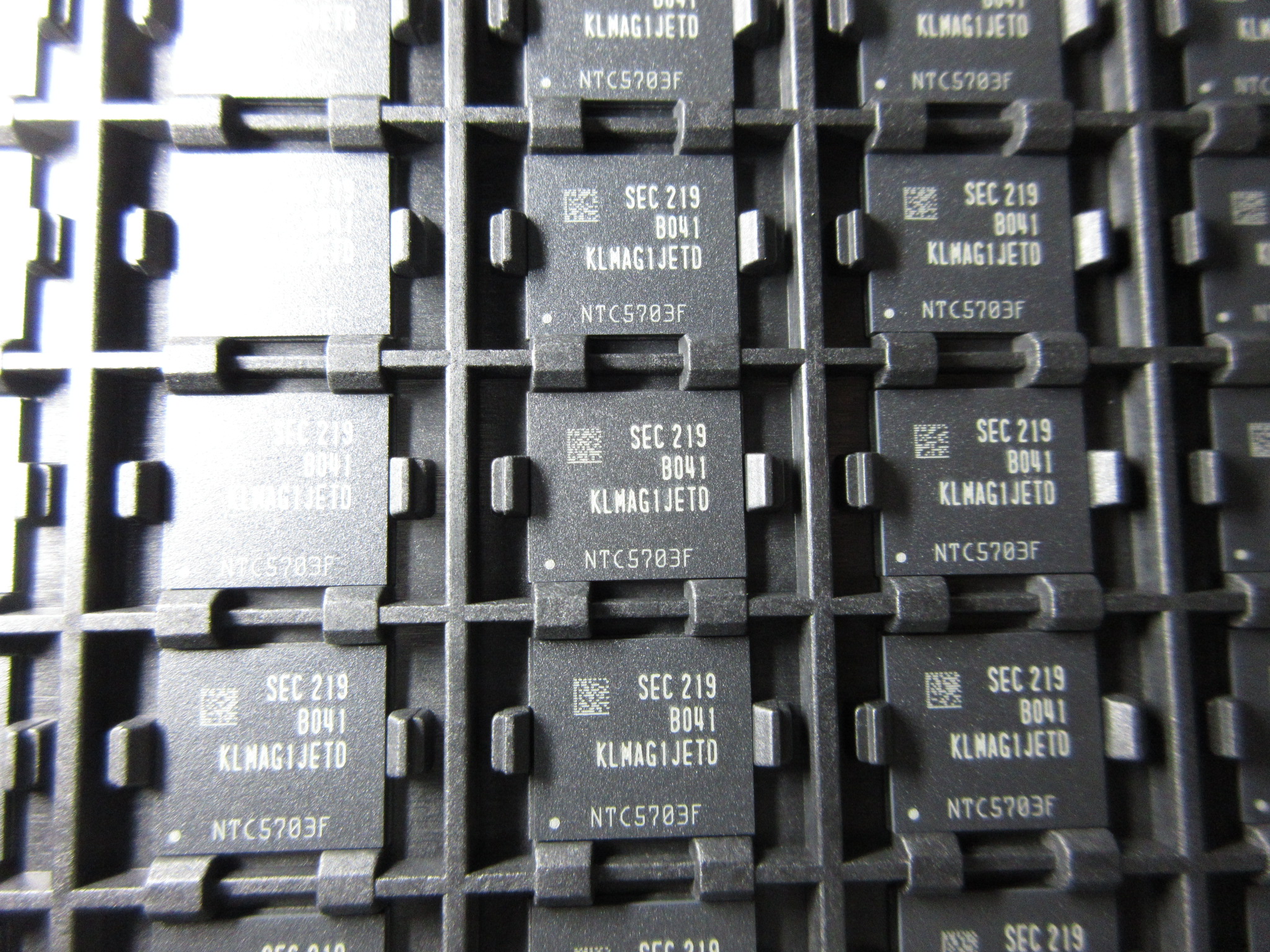

KLMAG1JETD-B041

eMMC5.1

16GB

1.8,3.3V/3.3V

HS400

11.5x13x0.8mm

-25~85°C

MassProduction

KLMAG2GEND-B031

eMMC5.0

16GB

1.8/3.3V

HS400

11.5x13x0.8mm

-25~85°C

EOL

KLMAG2GEND-B041

eMMC5.1

16GB

1.8/3.3V

HS400

11.5x13x0.8mm

-25~85°C

EOL

KLMAG2GESD-B03P

eMMC5.0

16GB

1.8/3.3V

HS400

11.5x13x0.8mm

-40~85°C

MassProduction

KLMAG2GESD-B03Q

eMMC5.0

16GB

1.8/3.3V

HS400

11.5x13x0.8mm

-40~105°C

MassProduction

KLMAG2GESD-B04P

eMMC5.1

16GB

1.8/3.3V

HS400

11.5x13x0.8mm

-40~85°C

MassProduction

KLMAG2GESD-B04Q

eMMC5.1

16GB

1.8/3.3V

HS400

11.5x13x0.8mm

-40~105°C

MassProduction

KLMAG2WEPD-B031

eMMC5.0

16GB

1.8/3.3V

HS400

11.5x13x0.8mm

-25~85°C

EOL

KLMBG2JENB-B041

eMMC5.1

32GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

EOL

KLMBG2JETD-B041

eMMC5.1

32GB

1.8,3.3V/3.3V

HS400

11.5x13x0.8mm

-25~85°C

MassProduction

KLMBG4GEND-B031

eMMC5.0

32GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

EOL

KLMBG4GEND-B041

eMMC5.1

32GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

EOL

KLMBG4GESD-B03P

eMMC5.0

32GB

1.8/3.3V

HS400

11.5x13x1.0mm

-40~85°C

MassProduction

KLMBG4GESD-B03Q

eMMC5.0

32GB

1.8/3.3V

HS400

11.5x13x1.0mm

-40~105°C

MassProduction

KLMBG4GESD-B04P

eMMC5.1

32GB

1.8/3.3V

HS400

11.5x13x1.0mm

-40~85°C

MassProduction

KLMBG4GESD-B04Q

eMMC5.1

32GB

1.8/3.3V

HS400

11.5x13x1.0mm

-40~85°C

MassProduction

KLMBG4WEBD-B031

eMMC5.0

32GB

1.8/3.3V

HS400

11.5x13x0.8mm

-25~85°C

EOL

KLMBG4WERD-B041

eMMC5.1

32GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

EOL

KLMCG2KETM-B041

eMMC5.1

64GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

EOL

KLMCG4JENB-B041

eMMC5.1

64GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

EOL

KLMCG4JETD-B041

eMMC5.1

64GB

1.8,3.3V/3.3V

HS400

11.5x13x1.0mm

-25~85°C

MassProduction

KLMCG4JEUD-B04P

eMMC5.1

64GB

1.8/3.3V

HS400

11.5x13x1.2mm

-40~85°C

Massproduction

KLMCG4JEUD-B04Q

eMMC5.1

64GB

1.8/3.3V

HS400

11.5x13x1.2mm

-40~105°C

Massproduction

KLMCG4VERF-B041

eMMC5.1

64GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

EOL

KLMCG8GEND-B031

eMMC5.0

64GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

EOL

KLMCG8GEND-B041

eMMC5.1

64GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

EOL

KLMCG8GESD-B03P

eMMC5.0

64GB

1.8/3.3V

HS400

11.5x13x1.0mm

-40~85°C

MassProduction

KLMCG8GESD-B03Q

eMMC5.0

64GB

1.8/3.3V

HS400

11.5x13x1.0mm

-40~105°C

MassProduction

KLMCG8GESD-B04P

eMMC5.1

64GB

1.8/3.3V

HS400

11.5x13x1.0mm

-40~85°C

MassProduction

KLMCG8GESD-B04Q

eMMC5.1

64GB

1.8/3.3V

HS400

11.5x13x1.0mm

-40~105°C

MassProduction

KLMCG8WEBD-B031

eMMC5.0

64GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

EOL

KLMDG4UERM-B041

eMMC5.1

128GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

EOL

KLMDG8JENB-B041

eMMC5.1

128GB

1.8/3.3V

HS400

11.5x13x1.2mm

-25~85°C

EOL

KLMDG8JEUD-B04P

eMMC5.1

128GB

1.8/3.3V

HS400

11.5x13x1.2mm

-40~85°C

Massproduction

KLMDG8JEUD-B04Q

eMMC5.1

128GB

1.8/3.3V

HS400

11.5x13x1.2mm

-40~105°C

Massproduction

KLMDG8VERF-B041

eMMC5.1

128GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

EOL

KLMDGAWEBD-B031

eMMC5.0

128GB

1.8/3.3V

HS400

11.5x13x1.4mm

-25~85°C

EOL

KLMEG8UERM-C041

eMMC5.1

256GB

1.8/3.3V

HS400

11.5x13x1.0mm

-25~85°C

EOL

Samsung UFS

Part number

Version

Capacity

VCC

接口

Package

Temperature

Production

KLUBG4G1ZF-C0CP

UFS2.1

32GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~95°C

MassProduction

KLUBG4G1ZF-C0CQ

UFS2.1

32GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~105°C

MassProduction

KLUCG4J1ZD-C0CP

UFS2.1

64GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~95°C

MassProduction

KLUCG4J1ZD-C0CQ

UFS2.1

64GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~105°C

MassProduction

KLUDG8J1ZD-C0CP

UFS2.1

128GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~95°C

MassProduction

KLUDG8J1ZD-C0CQ

UFS2.1

128GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~105°C

MassProduction

KLUEGAJ1ZD-C0CP

UFS2.1

256GB

1.8/3.3V

G32Lane

11.5x13x1.72mm

-40~95°C

MassProduction

KLUEGAJ1ZD-C0CQ

UFS2.1

256GB

1.8/3.3V

G32Lane

11.5x13x1.72mm

-40~105°C

MassProduction

KLUCG2UHYB-B0EP

UFS3.1

64GB

1.2/2.5V

G42Lane

11.5x13x1.2mm

-40~95°C

MassProduction

KLUCG2UHYB-B0EQ

UFS3.1

64GB

1.2/2.5V

G42Lane

11.5x13x1.2mm

-40~105°C

MassProduction

KLUDG4UHYB-B0EP

UFS3.1

128GB

1.2/2.5V

G42Lane

11.5x13x1.2mm

-40~95°C

MassProduction

KLUDG4UHYB-B0EQ

UFS3.1

128GB

1.2/2.5V

G42Lane

11.5x13x1.2mm

-40~105°C

MassProduction

KLUEG8UHYB-B0EP

UFS3.1

256GB

1.2/2.5V

G42Lane

11.5x13x1.2mm

-40~95°C

MassProduction

KLUEG8UHYB-B0EQ

UFS3.1

256GB

1.2/2.5V

G42Lane

11.5x13x1.2mm

-40~105°C

MassProduction

KLUFGAUHYB-B0EP

UFS3.1

512GB

1.2/2.5V

G42Lane

11.5x13x1.72mm

-40~95°C

MassProduction

KLUFGAUHYB-B0EQ

UFS3.1

512GB

1.2/2.5V

G42Lane

11.5x13x1.72mm

-40~105°C

MassProduction

KLUDG4UHDB-B2E1

UFS3.1

128GB

1.2/2.5V

G42Lane

11.5x13x0.8mm

-25~85°C

MassProduction

KLUDG4UHDC-B0E1

UFS3.1

128GB

1.2/2.5V

G42Lane

11.5x13x0.8mm

-25~85°C

MassProduction

KLUEG8UHDB-C2E1

UFS3.1

256GB

1.2/2.5V

G42Lane

11.5x13x1.0mm

-25~85°C

MassProduction

KLUEG8UHDC-B0E1

UFS3.1

256GB

1.2/2.5V

G42Lane

11.5x13x0.8mm

-25~85°C

MassProduction

KLUFG8RHDA-B2E1

UFS3.1

512GB

1.2/2.5V

G42Lane

11.5x13x1.0mm

-25~85°C

MassProduction

KLUFG8RHDB-B0E1

UFS3.1

512GB

1.2/2.5V

G42Lane

11.5x13x1.0mm

-25~85°C

MassProduction

KLUBG4G1CE-B0B1

UFS2.0

32GB

1.8/3.3V

G31Lane

11.5x13x1.0mm

-25~85°C

EOL

KLUBG4G1ZF-B0CP

UFS2.1

32GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~85°C

MassProduction

KLUBG4G1ZF-B0CQ

UFS2.1

32GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~105°C

MassProduction

KLUCG2K1EA-B0C1

UFS2.1

64GB

1.8/3.3V

G32Lane

11.5x13x1.0mm

-25~85°C

MassProduction

KLUCG2U1YB-B0CP

UFS2.1

64GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~85°C

MassProduction

KLUCG2U1YB-B0CQ

UFS2.1

64GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~105°C

MassProduction

KLUCG4J1BB-B0B1

UFS2.0

64GB

1.8/3.3V

G22Lane

11.5x13x1.0mm

-25~85°C

EOL

KLUCG4J1CB-B0B1

UFS2.0

64GB

1.8/3.3V

G31Lane

11.5x13x1.0mm

-25~85°C

EOL

KLUCG4J1ED-B0C1

UFS2.1

64GB

1.8/3.3V

G32Lane

11.5x13x1.0mm

-25~85°C

MassProduction

KLUCG4J1ZD-B0CP

UFS2.1

64GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~85°C

MassProduction

KLUCG4J1ZD-B0CQ

UFS2.1

64GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~105°C

MassProduction

KLUDG4U1EA-B0C1

UFS2.1

128GB

1.8/3.3V

G32Lane

11.5x13x1.0mm

-25~85°C

MassProduction

KLUDG4U1FB-B0C1

UFS2.1

128GB

1.8/3.3V

G32Lane

11.5x13x1.0mm

-25~85°C

MassProduction

KLUDG4U1YB-B0CP

UFS2.1

128GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~85°C

MassProduction

KLUDG4U1YB-B0CQ

UFS2.1

128GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~105°C

MassProduction

KLUDG8J1BB-B0B1

UFS2.0

128GB

1.8/3.3V

G22Lane

11.5x13x1.2mm

-25~85°C

EOL

KLUDG8J1CB-B0B1

UFS2.0

128GB

1.8/3.3V

G31Lane

11.5x13x1.2mm

-25~85°C

EOL

KLUDG8J1ZD-B0CP

UFS2.1

128GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~85°C

MassProduction

KLUDG8J1ZD-B0CQ

UFS2.1

128GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~105°C

MassProduction

KLUDG8V1EE-B0C1

UFS2.1

128GB

1.8/3.3V

G32Lane

11.5x13x1.0mm

-25~85°C

EOL

KLUEG8U1EA-B0C1

UFS2.1

256GB

1.8/3.3V

G32Lane

11.5x13x1.0mm

-25~85°C

MassProduction

KLUEG8U1EM-B0B1

UFS2.0

256GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-25~85°C

EOL

KLUEG8U1EM-B0C1

UFS2.1

256GB

1.8/3.3V

G32Lane

11.5x13x1.0mm

-25~85°C

EOL

KLUEG8U1YB-B0CP

UFS2.1

256GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~85°C

MassProduction

KLUEG8U1YB-B0CQ

UFS2.1

256GB

1.8/3.3V

G32Lane

11.5x13x1.2mm

-40~105°C

MassProduction

KLUEGAJ1ZD-B0CP

UFS2.1

256GB

1.8/3.3V

G32Lane

11.5x13x1.72mm

-40~85°C

MassProduction

KLUEGAJ1ZD-B0CQ

UFS2.1

256GB

1.8/3.3V

G32Lane

11.5x13x1.72mm

-40~105°C

MassProduction

KLUFG8R1EM-B0C1

UFS2.1

512GB

1.8/3.3V

G32Lane

11.5x13x1.0mm

-25~85°C

MassProduction

KLUGGAR1FA-B2C1

UFS2.1

1TB

1.8/3.3V

G32Lane

11.5x13x1.4mm

-25~85°C

MassProduction

KLUGGARHDA-B0D1

UFS3.0

1TB

1.2/2.5V

G42Lane

11.5x13x1.25mm

-25~85°C

MassProduction

Samsung LPDDR5X

Part Number

Capacity

Rate

VCC

Temperature

Package

K3KL3L30CM-BGCT

64Gb

x64

7500Mbps

1.8/1.05/0.9/0.5V

-25~85°C

496FBGA

K3KL3L30CM-JGCT

64Gb

x64

7500Mbps

1.8/1.05/0.9/0.5V

-25~85°C

441FBGA

K3KL3L30CM-MGCT

64Gb

x32

7500Mbps

1.8/1.05/0.9/0.5V

-25~85°C

315FBGA

K3KL4L40DM-BGCT

96Gb

x64

7500Mbps

1.8/1.05/0.9/0.5V

-25~85°C

496FBGA

K3KL5L50CM-BGCT

128Gb

x64

7500Mbps

1.8/1.05/0.9/0.5V

-25~85°C

496FBGA

K3KL5L50CM-MGCT

128Gb

x32

7500Mbps

1.8/1.05/0.9/0.5V

-25~85°C

315FBGA

K3KL8L80CM-MGCT

32Gb

x32

7500Mbps

1.8/1.05/0.9/0.5V

-25~85°C

315FBGA

SamsungLPDDR5

Part Number

Capacity

架构

Rate

VCC

Temperature

Package

Production

K3LK2K20BM-BGCN

48Gb

x64

5500Mbps

1.8/1.05/0.9/0.5V

-25~85°C

496FBGA

Sample

Samsung LPDDR4x

Part Number

架构

Rate

VCC

Temperature

Package

Production

K3UH5H50AM-JGCR

x64

4266Mbps

1.8/1.1/0.6V

-25~85°C

432FBGA

Sample

K3UH7H70AM-JGCR

x64

4266Mbps

1.8/1.1/0.6V

-25~85°C

432FBGA

Sample

K4U6E3S4AA-MGCR

x32

4266Mbps

1.8/1.1/0.6V

-25~85°C

200FBGA

Sample

K4UBE3D4AA-MGCR

x32

4266Mbps

1.8/1.1/0.6V

-25~85°C

200FBGA

Sample

K4UCE3Q4AA-MGCR

x32

4266Mbps

1.8/1.1/0.6V

-25~85°C

200FBGA

Sample

K3UH5H50AM-JGCL

x64

4266Mbps

1.8/1.1/0.6V

-25~85°C

432FBGA

MassProduction

K3UH7H70AM-JGCL

x64

4266Mbps

1.8/1.1/0.6V

-25~85°C

432FBGA

MassProduction

K3UHAHA0AM-AGCL

x64

4266Mbps

1.8/1.1/0.6V

-25~85°C

556FBGA

MassProduction

K4U6E3S4AA-MGCL

x32

4266Mbps

1.8/1.1/0.6V

-25~85°C

200FBGA

MassProduction

K4UBE3D4AA-MGCL

x32

4266Mbps

1.8/1.1/0.6V

-25~85°C

200FBGA

MassProduction

K4UCE3Q4AA-MGCL

x32

4266Mbps

1.8/1.1/0.6V

-25~85°C

200FBGA

MassProduction

K4U8E3S4AD-GFCL

x32

4266Mbps

1.8/1.1/0.6V

-40~95°C

200FBGA

MassProduction

K4U8E3S4AD-GHCL

x32

4266Mbps

1.8/1.1/0.6V

-40~105°C

200FBGA

MassProduction

K4U8E3S4AD-GUCL

x32

4266Mbps

1.8/1.1/0.6V

-40~125°C

200FBGA

MassProduction

K3UH5H50AM-AGCL

x64

4266Mbps

1.8/1.1/0.6V

-25~85°C

556FBGA

批量生产

K3UH6H60BM-AGCL

x64

4266Mbps

1.8/1.1/0.6V

-25~85°C

556FBGA

MassProduction

K3UH7H70AM-AGCL

x64

4266Mbps

1.8/1.1/0.6V

-25~85°C

556FBGA

MassProduction

K4U2E3S4AA-GFCL

x32

4266Mbps

1.8/1.1/0.6V

-40~95°C

200FBGA

MassProduction

K4U2E3S4AA-GHCL

x32

4266Mbps

1.8/1.1/0.6V

-40~105°C

200FBGA

MassProduction

K4U2E3S4AA-GUCL

x32

4266Mbps

1.8/1.1/0.6V

-40~125°C

200FBGA

MassProduction

K4U6E3S4AM-GFCL

x32

4266Mbps

1.8/1.1/0.6V

-40~95°C

200FBGA

MassProduction

K4U6E3S4AM-GHCL

x32

4266Mbps

1.8/1.1/0.6V

-40~105°C

200FBGA

MassProduction

K4U6E3S4AM-GUCL

x32

4266Mbps

1.8/1.1/0.6V

-40~125°C

200FBGA

MassProduction

K4UBE3D4AM-GFCL

x32

4266Mbps

1.8/1.1/0.6V

-40~95°C

200FBGA

MassProduction

K4UBE3D4AM-GHCL

x32

4266Mbps

1.8/1.1/0.6V

-40~105°C

200FBGA

Sample

K4UBE3D4AM-GUCL

x32

4266Mbps

1.8/1.1/0.6V

-40~125°C

200FBGA

MassProduction

K4UHE3D4AA-GFCL

x32

4266Mbps

1.8/1.1/0.6V

-40~95°C

200FBGA

MassProduction

K4UHE3D4AA-GHCL

x32

4266Mbps

1.8/1.1/0.6V

-40~105°C

200FBGA

Sample

K4UHE3D4AA-GUCL

x32

4266Mbps

1.8/1.1/0.6V

-40~125°C

200FBGA

MassProduction

Samsung LPDDR4

Part Number

架构

Rate

VCC

Temperature

Package

Production

K4F2E3S4HA-TFCL

x32

4266Mbps

1.8/1.1/1.1V

-40~95°C

200FBGA

MassProduction

K4F2E3S4HA-THCL

x32

4266Mbps

1.8/1.1/1.1V

-40~105°C

200FBGA

MassProduction

K4F2E3S4HA-TUCL

x32

4266Mbps

1.8/1.1/1.1V

-40~125°C

200FBGA

MassProduction

K4F6E3S4HM-TFCL

x32

4266Mbps

1.8/1.1/1.1V

-40~95°C

200FBGA

MassProduction

K4F6E3S4HM-THCL

x32

4266Mbps

1.8/1.1/1.1V

-40~105°C

200FBGA

MassProduction

K4F6E3S4HM-TUCL

x32

4266Mbps

1.8/1.1/1.1V

-40~125°C

200FBGA

MassProduction

K4FBE3D4HM-TFCL

x32

4266Mbps

1.8/1.1/1.1V

-40~95°C

200FBGA

MassProduction

K4FBE3D4HM-THCL

x32

4266Mbps

1.8/1.1/1.1V

-40~105°C

200FBGA

MassProduction

K4FBE3D4HM-TUCL

x32

4266Mbps

1.8/1.1/1.1V

-40~125°C

200FBGA

MassProduction

K4FHE3D4HA-TFCL

x32

4266Mbps

1.8/1.1/1.1V

-40~95°C

200FBGA

MassProduction

K4FHE3D4HA-THCL

x32

4266Mbps

1.8/1.1/1.1V

-40~105°C

200FBGA

MassProduction

K4FHE3D4HA-TUCL

x32

4266Mbps

1.8/1.1/1.1V

-40~125°C

200FBGA

MassProduction

K4F6E304HB-MGCJ

x32

3733Mbps

1.8/1.1/1.1V

-25~85°C

200FBGA

MassProduction

K4F6E3S4HM-MGCJ

x32

3733Mbps

1.8/1.1/1.1V

-25~85°C

200FBGA

MassProduction

K4F8E3S4HD-MGCL

x32

4266Mbps

1.8/1.1/1.1V

-25~85°C

200FBGA

MassProduction

K4F8E3S4HD-GFCL

x32

4266Mbps

1.8/1.1/1.1V

-40~95°C

200FBGA

MassProduction

K4F8E3S4HD-GHCL

x32

4266Mbps

1.8/1.1/1.1V

-40~105°C

200FBGA

MassProduction

K4F8E3S4HD-GUCL

x32

4266Mbps

1.8/1.1/1.1V

-40~125°C

200FBGA

MassProduction

K4F2E3S4HA-GFCL

x32

4266Mbps

1.8/1.1/1.1V

-40~95°C

200FBGA

MassProduction

K4F2E3S4HA-GHCL

x32

4266Mbps

1.8/1.1/1.1V

-40~105°C

200FBGA

MassProduction

K4F2E3S4HA-GUCL

x32

4266Mbps

1.8/1.1/1.1V

-40~125°C

200FBGA

MassProduction

K4F2E3S4HM-MFCJ

x32

3733Mbps

1.8/1.1/1.1V

-40~95°C

200FBGA

MassProduction

K4F2E3S4HM-MHCJ

x32

3733Mbps

1.8/1.1/1.1V

-40~105°C

200FBGA

MassProduction

K4F4E3S4HF-GFCJ

x32

3733Mbps

1.8/1.1/1.1V

-40~95°C

200FBGA

MassProduction

K4F4E3S4HF-GHCJ

x32

3733Mbps

1.8/1.1/1.1V

-40~105°C

200FBGA

MassProduction

K4F4E3S4HF-GUCJ

x32

3733Mbps

1.8/1.1/1.1V

-40~125°C

200FBGA

MassProduction

K4F6E3D4HB-MFCJ

x32

3733Mbps

1.8/1.1/1.1V

-40~95°C

200FBGA

MassProduction

K4F6E3D4HB-MHCJ

x32

3733Mbps

1.8/1.1/1.1V

-40~105°C

200FBGA

MassProduction

K4F6E3S4HM-GFCL

x32

4266Mbps

1.8/1.1/1.1V

-40~95°C

200FBGA

MassProduction

K4F6E3S4HM-GHCL

x32

4266Mbps

1.8/1.1/1.1V

-40~105°C

200FBGA

MassProduction

K4F6E3S4HM-GUCL

x32

4266Mbps

1.8/1.1/1.1V

-40~125°C

200FBGA

MassProduction

K4F8E3S4HB-MFCJ

x32

3733Mbps

1.8/1.1/1.1V

-40~95°C

200FBGA

MassProduction

K4F8E3S4HB-MHCJ

x32

3733Mbps

1.8/1.1/1.1V

-40~105°C

200FBGA

MassProduction

K4FBE3D4HM-GFCL

x32

4266Mbps

1.8/1.1/1.1V

-40~95°C

200FBGA

MassProduction

K4FBE3D4HM-GHCL

x32

4266Mbps

1.8/1.1/1.1V

-40~105°C

200FBGA

MassProduction

K4FBE3D4HM-GUCL

x32

4266Mbps

1.8/1.1/1.1V

-40~125°C

200FBGA

MassProduction

K4FHE3D4HA-GFCL

x32

4266Mbps

1.8/1.1/1.1V

-40~95°C

200FBGA

MassProduction

K4FHE3D4HA-GHCL

x32

4266Mbps

1.8/1.1/1.1V

-40~105°C

200FBGA

MassProduction

K4FHE3D4HA-GUCL

x32

4266Mbps

1.8/1.1/1.1V

-40~125°C

200FBGA

MassProduction

K4FHE3D4HM-MFCJ

x32

3733Mbps

1.8/1.1/1.1V

-40~95°C

200FBGA

MassProduction

K4FHE3D4HM-MHCJ

x32

3733Mbps

1.8/1.1/1.1V

-40~105°C

200FBGA

MassProduction

Samsung LPDDR3

Part Number

Capacity

架构

Rate

VCC

Temperature

Package

production

K4E6E304EC-EGCG

16Gb

x32

2133Mbps

1.8/1.2/1.2V

-25~85°C

178FBGA

MassProduction

K4E8E324EB-EGCG

8Gb

x32

2133Mbps

1.8/1.2/1.2V

-25~85°C

178FBGA

MassProduction

K4EBE304EC-EGCG

32Gb

x32

2133Mbps

1.8/1.2/1.2V

-25~85°C

178FBGA

MassProduction

K4E6E304ED-EGCG

16Gb

x32

2133Mbps

1.8/1.2/1.2V

-25~85°C

178FBGA

MassProduction

K4E8E324ED-EGCG

8Gb

x32

2133Mbps

1.8/1.2/1.2V

-25~85°C

178FBGA

MassProduction

K4EBE304ED-EGCG

32Gb

x32

2133Mbps

1.8/1.2/1.2V

-25~85°C

178FBGA

MassProduction

Samsung DDR3

Part Number

Capacity

架构

Rate

VCC

Temperature

Package

Production

K4B1G1646I-BYNB

1Gb

64Mx16

2133Mbps

1.35V

0~85°C

96FBGA

MassProduction

K4B2G1646F-BYNB

2Gb

128Mx16

2133Mbps

1.35V

0~85°C

96FBGA

MassProduction

K4B4G0846E-YCK0

4Gb

512Mx8

1600Mbps

1.35V

0~85°C

78FBGA

MassProduction

K4B4G0846E-YCMA

4Gb

512Mx8

1866Mbps

1.35V

0~85°C

78FBGA

MassProduction

K4B4G1646E-YCK0

4Gb

512Mx8

1600Mbps

1.35V

0~85°C

96FBGA

MassProduction

K4B4G1646E-YCMA

4Gb

512Mx8

1866Mbps

1.35V

0~85°C

96FBGA

MassProduction

K4B8G0846D-MMMA

8Gb

1Gx8

1866Mbps

1.35V

-40~95°C

78FBGA

EOL

K4B8G1646D-MMMA

8Gb

512Mx16

1866Mbps

1.35V

0~85°C

96FBGA

EOL

K4B1G0846I-BYNB

1Gb

128Mx8

2133Mbps

1.35V

0~85°C

78FBGA

MassProduction

K4B8G0846D-MCK0

8Gb

1Gx8

1600Mbps

1.5V

0~85°C

78FBGA

EOL

K4B8G0846D-MCMA

8Gb

1Gx8

1866Mbps

1.5V

0~85°C

78FBGA

EOL

K4B8G0846D-MCNB

8Gb

1Gx8

2133Mbps

1.5V

0~85°C

78FBGA

EOL

K4B8G0846D-MMK0

8Gb

1Gx8

1600Mbps

1.35V

-40~95°C

78FBGA

EOL

K4B8G0846D-MYK0

8Gb

1Gx8

1600Mbps

1.35V

0~85°C

78FBGA

EOL

K4B8G0846D-MYMA

8Gb

1Gx8

1866Mbps

1.35V

0~85°C

78FBGA

EOL

K4B8G1646D-MCK0

8Gb

512Mx16

1600Mbps

1.5V

0~85°C

96FBGA

EOL

K4B8G1646D-MCMA

8Gb

512Mx16

1866Mbps

1.5V

0~85°C

96FBGA

EOL

K4B8G1646D-MCNB

8Gb

512Mx16

2133Mbps

1.5V

0~85°C

96FBGA

EOL

K4B8G1646D-MMK0

8Gb

512Mx16

1600Mbps

1.35V

0~85°C

96FBGA

EOL

K4B8G1646D-MYK0

8Gb

512Mx16

1600Mbps

1.35V

-40~95°C

96FBGA

EOL

K4B8G1646D-MYMA

8Gb

512Mx16

1866Mbps

1.35V

-40~95°C

96FBGA

EOL

K4B1G0846I-BCK0

1Gb

128Mx8

1600Mbps

1.5V

0~85°C

78FBGA

MassProduction

K4B1G0846I-BCMA

1Gb

128Mx8

1866Mbps

1.5V

0~85°C

78FBGA

MassProduction

K4B1G0846I-BCNB

1Gb

128Mx8

2133Mbps

1.5V

0~85°C

78FBGA

MassProduction

K4B1G0846I-BMK0

1Gb

128Mx8

1600Mbps

1.35V

-40~95°C

78FBGA

MassProduction

K4B1G0846I-BMMA

1Gb

128Mx8

1600Mbps

1.35V

-40~95°C

78FBGA

MassProduction

K4B1G0846I-BYK0

1Gb

128Mx8

1600Mbps

1.35V

0~85°C

78FBGA

MassProduction

K4B1G0846I-BYMA

1Gb

128Mx8

1866Mbps

1.35V

0~85°C

78FBGA

MassProduction

K4B1G1646I-BCK0

1Gb

64Mx16

1600Mbps

1.5V

0~85°C

96FBGA

MassProduction

K4B1G1646I-BCMA

1Gb

64Mx16

1866Mbps

1.5V

0~85°C

96FBGA

MassProduction

K4B1G1646I-BCNB

1Gb

64Mx16

2133Mbps

1.5V

0~85°C

96FBGA

MassProduction

K4B1G1646I-BFMA

1Gb

64Mx16

1866Mbps

1.35V

-40~95°C

96FBGA

MassProduction

K4B1G1646I-BHMA

1Gb

64Mx16

1866Mbps

1.35V

-40~105°C

96FBGA

MassProduction

K4B1G1646I-BMK0

1Gb

64Mx16

1600Mbps

1.35V

-40~95°C

96FBGA

MassProduction

K4B1G1646I-BMMA

1Gb

64Mx16

1600Mbps

1.35V

-40~95°C

96FBGA

MassProduction

K4B1G1646I-BYK0

1Gb

64Mx16

1600Mbps

1.35V

0~85°C

96FBGA

MassProduction

K4B1G1646I-BYMA

1Gb

64Mx16

1866Mbps

1.35V

0~85°C

96FBGA

MassProduction

K4B2G0846F-BCK0

2Gb

256Mx8

1600Mbps

1.5V

0~85°C

78FBGA

MassProduction

K4B2G0846F-BCMA

2Gb

256Mx8

1866Mbps

1.5V

0~85°C

78FBGA

MassProduction

K4B2G0846F-BCNB

2Gb

256Mx8

2133Mbps

1.5V

0~85°C

78FBGA

MassProduction

K4B2G0846F-BMK0

2Gb

256Mx8

1600Mbps

1.35V

-40~95°C

78FBGA

MassProduction

K4B2G0846F-BMMA

2Gb

256Mx8

1600Mbps

1.35V

-40~95°C

78FBGA

MassProduction

K4B2G0846F-BYK0

2Gb

256Mx8

1600Mbps

1.35V

0~85°C

78FBGA

MassProduction

K4B2G0846F-BYMA

2Gb

256Mx8

1866Mbps

1.35V

0~85°C

78FBGA

MassProduction

K4B2G0846F-BYNB

2Gb

256Mx8

2133Mbps

1.35V

0~85°C

78FBGA

MassProduction

K4B2G1646F-BCK0

2Gb

128Mx16

1600Mbps

1.5V

0~85°C

96FBGA

MassProduction

K4B2G1646F-BCMA

2Gb

128Mx16

1866Mbps

1.5V

0~85°C

96FBGA

MassProduction

K4B2G1646F-BCNB

2Gb

128Mx16

2133Mbps

1.5V

0~85°C

96FBGA

MassProduction

K4B2G1646F-BFMA

2Gb

128Mx16

1866Mbps

1.35V

-40~95°C

96FBGA

MassProduction

K4B2G1646F-BHMA

2Gb

128Mx16

1866Mbps

1.35V

-40~105°C

96FBGA

MassProduction

K4B2G1646F-BMK0

2Gb

128Mx16

1600Mbps

1.35V

-40~95°C

96FBGA

MassProduction

K4B2G1646F-BMMA

2Gb

128Mx16

1600Mbps

1.35V

-40~95°C

96FBGA

MassProduction

K4B2G1646F-BYK0

2Gb

128Mx16

1600Mbps

1.35V

0~85°C

96FBGA

MassProduction

K4B2G1646F-BYMA

2Gb

128Mx16

1866Mbps

1.35V

0~85°C

96FBGA

MassProduction

K4B4G0846D-BCH9

4Gb

512Mx8

1333Mbps

1.5V

0~85°C

78FBGA

MassProduction

K4B4G0846D-BCK0

4Gb

512Mx8

1600Mbps

1.5V

0~85°C

78FBGA

MassProduction

K4B4G0846D-BCMA

4Gb

512Mx8

1866Mbps

1.5V

0~85°C

78FBGA

MassProduction

K4B4G0846D-BCNB

4Gb

512Mx8

2133Mbps

1.5V

0~85°C

78FBGA

MassProduction

K4B4G0846D-BMK0

4Gb

512Mx8

1600Mbps

1.35V

-40~95°C

78FBGA

MassProduction

K4B4G0846D-BMMA

4Gb

512Mx8

1600Mbps

1.35V

-40~95°C

78FBGA

MassProduction

K4B4G0846D-BYH9

4Gb

512Mx8

1333Mbps

1.35V

0~85°C

78FBGA

MassProduction

K4B4G0846D-BYK0

4Gb

512Mx8

1600Mbps

1.35V

0~85°C

78FBGA

MassProduction

K4B4G0846D-BYMA

4Gb

512Mx8

1866Mbps

1.35V

0~85°C

78FBGA

MassProduction

K4B4G0846D-BYNB

4Gb

512Mx8

2133Mbps

1.35V

0~85°C

78FBGA

MassProduction

K4B4G0846E-BCK0

4Gb

512Mx8

1600Mbps

1.5V

0~85°C

78FBGA

MassProduction

K4B4G0846E-BCMA

4Gb

512Mx8

1866Mbps

1.5V

0~85°C

78FBGA

MassProduction

K4B4G0846E-BMK0

4Gb

512Mx8

1600Mbps

1.35V

-40~95°C

78FBGA

MassProduction

K4B4G0846E-BMMA

4Gb

512Mx8

1600Mbps

1.35V

-40~95°C

78FBGA

MassProduction

K4B4G0846E-BYK0

4Gb

512Mx8

1600Mbps

1.35V

0~85°C

78FBGA

MassProduction

K4B4G0846E-BYMA

4Gb

512Mx8

1866Mbps

1.35V

0~85°C

78FBGA

MassProduction

K4B4G0846R-BFMA

4Gb

512Mx8

1866Mbps

1.35V

-40~95°C

78FBGA

MassProduction

K4B4G0846R-BHMA

4Gb

512Mx8

1866Mbps

1.35V

-40~105°C

78FBGA

MassProduction

K4B4G1646D-BCH9

4Gb

256Mx16

1333Mbps

1.5V

0~85°C

96FBGA

MassProduction

K4B4G1646D-BCK0

4Gb

256Mx16

1600Mbps

1.5V

0~85°C

96FBGA

MassProduction

K4B4G1646D-BCMA

4Gb

256Mx16

1866Mbps

1.5V

0~85°C

96FBGA

MassProduction

K4B4G1646D-BCNB

4Gb

256Mx16

2133Mbps

1.5V

0~85°C

96FBGA

MassProduction

K4B4G1646D-BFMA

4Gb

256Mx16

1866Mbps

1.35V

-40~95°C

96FBGA

MassProduction

K4B4G1646D-BHMA

4Gb

256Mx16

1866Mbps

1.35V

-40~105°C

96FBGA

MassProduction

K4B4G1646D-BMK0

4Gb

256Mx16

1600Mbps

1.35V

-40~95°C

96FBGA

MassProduction

K4B4G1646D-BMMA

4Gb

256Mx16

1600Mbps

1.35V

-40~95°C

96FBGA

MassProduction

K4B4G1646D-BYH9

4Gb

256Mx16

1333Mbps

1.35V

0~85°C

96FBGA

MassProduction

K4B4G1646D-BYK0

4Gb

256Mx16

1600Mbps

1.35V

0~85°C

96FBGA

MassProduction

K4B4G1646D-BYMA

4Gb

256Mx16

1866Mbps

1.35V

0~85°C

96FBGA

MassProduction

K4B4G1646D-BYNB

4Gb

256Mx16

2133Mbps

1.35V

0~85°C

96FBGA

MassProduction

K4B4G1646E-BCK0

4Gb

512Mx8

1600Mbps

1.5V

0~85°C

96FBGA

MassProduction

K4B4G1646E-BCMA

4Gb

512Mx8

1866Mbps

1.5V

0~85°C

96FBGA

MassProduction

K4B4G1646E-BMK0

4Gb

256Mx16

1600Mbps

1.35V

-40~95°C

96FBGA

MassProduction

K4B4G1646E-BMMA

4Gb

256Mx16

1600Mbps

1.35V

-40~95°C

96FBGA

MassProduction

K4B4G1646E-BYK0

4Gb

512Mx8

1600Mbps

1.35V

0~85°C

96FBGA

MassProduction

K4B4G1646E-BYMA

4Gb

512Mx8

1866Mbps

1.35V

0~85°C

96FBGA

MassProduction

Samsung DDR4

Part Number

Capacity

架构

Rate

VCC

Temperature

Package

Production

K4AAG085WA-BCWE

16Gb

2Gx8

3200Mbps

1.2V

0~85°C

78FBGA

Sample

K4AAG165WA-BCWE

16Gb

1Gx16

3200Mbps

1.2V

0~85°C

96FBGA

Sample

K4ABG085WA-MCWE

32Gb

4Gx8

3200Mbps

1.2V

0~85°C

78FBGA

Sample

K4ABG165WA-MCWE

32Gb

2Gx16

3200Mbps

1.2V

0~85°C

96FBGA

Sample

K4A4G085WF-BCTD

4Gb

512Mx8

2666Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A4G085WF-BITD

4Gb

512Mx8

2666Mbps

1.2V

-40~95°C

78FBGA

Sample

K4A4G165WE-BCWE

4Gb

256Mx16

3200Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4A4G165WF-BCTD

4Gb

256Mx16

2666Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4A4G165WF-BITD

4Gb

256Mx16

2666Mbps

1.2V

-40~95°C

96FBGA

Sample

K4A8G085WC-BCWE

8Gb

1Gx8

3200Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A8G085WC-BITD

8Gb

1Gx8

2666Mbps

1.2V

-40~95°C

78FBGA

MassProduction

K4A8G085WC-BIWE

8Gb

1Gx8

3200Mbps

1.2V

-40~95°C

78FBGA

MassProduction

K4A8G165WB-BCWE

8Gb

512Mx16

3200Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4A8G165WC-BCWE

8Gb

512Mx16

3200Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4A8G165WC-BITD

8Gb

512Mx16

2666Mbps

1.2V

-40~95°C

96FBGA

MassProduction

K4A8G165WC-BIWE

8Gb

512Mx16

3200Mbps

1.2V

-40~95°C

96FBGA

MassProduction

K4AAG085WA-BCTD

16Gb

2Gx8

2666Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4ABG085WA-MCTD

32Gb

4Gx8

2666Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4ABG165WA-MCTD

32Gb

2Gx16

2666Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4AAG085WB-MCPB

16Gb

2Gx8

2133Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4AAG085WB-MCRC

16Gb

2Gx8

2400Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4AAG165WA-BCTD

16Gb

1Gx16

2666Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4AAG165WB-MCPB

16Gb

1Gx16

2133Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4AAG165WB-MCRC

16Gb

1Gx16

2400Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4AAG165WB-MCTD

16Gb

1Gx16

2666Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4A4G045WE-BCPB

4Gb

1Gx4

2133Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A4G045WE-BCRC

4Gb

1Gx4

2400Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A4G045WE-BCTD

4Gb

1Gx4

2666Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A4G085WE-BCPB

4Gb

512Mx8

2133Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A4G085WE-BCRC

4Gb

512Mx8

2400Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A4G085WE-BCTD

4Gb

512Mx8

2666Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A4G085WE-BIRC

4Gb

512Mx8

2400Mbps

1.2V

-40~95°C

78FBGA

MassProduction

K4A4G085WE-BITD

4Gb

512Mx8

2666Mbps

1.2V

-40~95°C

78FBGA

MassProduction

K4A4G165WE-BCPB

4Gb

256Mx16

2133Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4A4G165WE-BCRC

4Gb

256Mx16

2400Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4A4G165WE-BCTD

4Gb

256Mx16

2666Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4A4G165WE-BIRC

4Gb

256Mx16

2400Mbps

1.2V

-40~95°C

96FBGA

MassProduction

K4A4G165WE-BITD

4Gb

256Mx16

2666Mbps

1.2V

-40~95°C

96FBGA

MassProduction

K4A4G165WE-BIWE

4Gb

256Mx16

3200Mbps

1.2V

-40~95°C

96FBGA

MassProduction

K4A8G045WB-BCPB

8Gb

2Gx4

2133Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A8G045WB-BCRC

8Gb

2Gx4

2400Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A8G045WB-BCTD

8Gb

2Gx4

2666Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A8G045WC-BCPB

8Gb

2Gx4

2133Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A8G045WC-BCRC

8Gb

2Gx4

2400Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A8G045WC-BCTD

8Gb

2Gx4

2666Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A8G085WB-BCPB

8Gb

1Gx8

2133Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A8G085WB-BCRC

8Gb

1Gx8

2400Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A8G085WB-BCTD

8Gb

1Gx8

2666Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A8G085WB-BIRC

8Gb

1Gx8

2400Mbps

1.2V

-40~95°C

78FBGA

MassProduction

K4A8G085WB-BITD

8Gb

1Gx8

2666Mbps

1.2V

-40~95°C

78FBGA

MassProduction

K4A8G085WC-BCPB

8Gb

1Gx8

2133Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A8G085WC-BCRC

8Gb

1Gx8

2400Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A8G085WC-BCTD

8Gb

1Gx8

2666Mbps

1.2V

0~85°C

78FBGA

MassProduction

K4A8G165WB-BCPB

8Gb

512Mx16

2133Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4A8G165WB-BCRC

8Gb

512Mx16

2400Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4A8G165WB-BCTD

8Gb

512Mx16

2666Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4A8G165WB-BIRC

8Gb

512Mx16

2400Mbps

1.2V

-40~95°C

96FBGA

MassProduction

K4A8G165WB-BITD

8Gb

512Mx16

2666Mbps

1.2V

-40~95°C

96FBGA

MassProduction

K4A8G165WB-BIWE

8Gb

512Mx16

3200Mbps

1.2V

-40~95°C

96FBGA

MassProduction

K4A8G165WC-BCPB

8Gb

512Mx16

2133Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4A8G165WC-BCRC

8Gb

512Mx16

2400Mbps

1.2V

0~85°C

96FBGA

MassProduction

K4A8G165WC-BCTD

8Gb

512Mx16

2666Mbps

1.2V

0~85°C

96FBGA

MassProduction

Samsung DDR5

Part Number

Apply

Capacity

架构

Rate

VCC

temperature

Package

Production

K4RAH086VB-BCWM

AI, Server, 5G & Connectivity

16 Gb

2G x 8

5600 Mbps

1.1 V

0 ~ 85 °C

82 FBGA

Mass Production

K4RAH086VB-BIQK

AI, Server, 5G & Connectivity

16 Gb

2G x 8

4800 Mbps

1.1 V

-40 ~ 95 °C

82 FBGA

Mass Production

K4RAH086VB-BIWM

AI, Server, 5G & Connectivity

16 Gb

2G x 8

5600 Mbps

1.1 V

-40 ~ 95 °C

82 FBGA

Mass Production

K4RAH086VP-BCWM

AI, Server, 5G & Connectivity, PC & Gaming

16 Gb

2G x 8

5600 Mbps

1.1 V

0 ~ 85 °C

82 FBGA

Mass Production

K4RAH165VB-BCWM

AI, Server, 5G & Connectivity

16 Gb

1G x 16

5600 Mbps

1.1 V

0 ~ 85 °C

106 FBGA

Mass Production

K4RAH165VB-BIQK

AI, Server, 5G & Connectivity

16 Gb

1G x 16

4800 Mbps

1.1 V

-40 ~ 95 °C

106 FBGA

Mass Production

K4RAH165VB-BIWM

AI, Server, 5G & Connectivity

16 Gb

1G x 16

5600 Mbps

1.1 V

-40 ~ 95 °C

106 FBGA

Mass Production

K4RAH165VP-BCWM

AI, Server, 5G & Connectivity, PC & Gaming

16 Gb

1G x 16

5600 Mbps

1.1 V

0 ~ 85 °C

106 FBGA

Mass Production

K4RHE086VB-BCWM

AI, Server, 5G & Connectivity, PC & Gaming

24 Gb

2G x 8

5600 Mbps

1.1 V

0 ~ 85 °C

82 FBGA

Mass Production

K4RHE165VB-BCWM

AI, Server, 5G & Connectivity, PC & Gaming

24 Gb

1G x 16

5600 Mbps

1.1 V

0 ~ 85 °C

106 FBGA

Mass Production

K4RCH046VM-2CLP

AI, Server, 5G & Connectivity

32 Gb

4G x 4

6400 Mbps

1.1 V

0 ~ 85 °C

78 FBGA

Sample

K4RBH046VM-BCCP

AI, Server, 5G & Connectivity

32 Gb

2G x 4

6400 Mbps

1.1 V

0 ~ 85 °C

78 FBGA

Sample

K4RCH046VM-2CCM

AI, Server, 5G & Connectivity

32 Gb

4G x 4

5600 Mbps

1.1 V

0 ~ 85 °C

78 FBGA

Sample

K4RBH046VM-BCWM

AI, Server, 5G & Connectivity

32 Gb

2G x 4

5600 Mbps

1.1 V

0 ~ 85 °C

78 FBGA

Sample

K4RAH086VB-BCQK

AI, Server, 5G & Connectivity

16 Gb

2G x 8

4800 Mbps

1.1 V

0 ~ 85 °C

82 FBGA

Mass Production

K4RAH165VB-BCQK

AI, Server, 5G & Connectivity

16 Gb

1G x 16

4800 Mbps

1.1 V

0 ~ 85 °C

106 FBGA

eMMC

MTFC128GAPALBH-AIT

128GB

WFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x1.1

Automotive

x8

MTFC128GAPALNS-AAT

128GB

TFBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

13x11.5x1.2

Automotive

x8

MTFC128GAPALNS-AIT

128GB

TFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x1.2

Automotive

x8

MTFC128GAXAQEA

128GB

WFBGA

3.3V

5.1

-25C to +85C

(Empty)

(Empty)

(Empty)

x8

MTFC128GAZAQJP-AAT

128GB

VFBGA

2.7V-3.6V

5.1

-40C to +105C

(Empty)

(Empty)

Automotive

x8

MTFC128GAZAQJP-AIT

128GB

VFBGA

2.7V-3.6V

5.1

-40C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC128GAZAQJP-IT

128GB

VFBGA

2.7V-3.6V

5.1

-40C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC16GAKAEDQ-AAT

16GB

LBGA

System.Object[]

5

-40C to +105C

100-ball

14 x 18 x 1.4

Automotive

x8

MTFC16GAKAEEF-AAT

16GB

TFBGA

System.Object[]

5

-40C to +105C

169-ball

14 x 18 x 1.2

Automotive

x8

MTFC16GAPALBH-AAT

16GB

TFBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

13x11.5x1.1

Automotive

x8

MTFC16GAPALBH-AIT

16GB

TFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x1.1

Automotive

x8

MTFC16GAPALBH-IT

16GB

TFBGA

3.3V

5.1

-40C to +85C

153-ball

11.5 x 13 x 1.1

(Empty)

x8

MTFC16GAPALGT-AAT

16GB

WFBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

13x11.5x0.8

Automotive

x8

MTFC16GAPALGT-AIT

16GB

WFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x0.8

Automotive

x8

MTFC16GAPALNA-AAT

16GB

TBGA

2.7V-3.6V

5.1

-40C to +105C

100-ball

18x14x1.2

Automotive

x8

MTFC16GAPALNA-AIT

16GB

TBGA

2.7V-3.6V

5.1

-40C to +85C

100-ball

18x14x1.2

Automotive

x8

MTFC256GBCAQTC-AAT

256GB

LFBGA

3.3V

5.1

-40C to +105C

(Empty)

(Empty)

(Empty)

x8

MTFC32GAKAEDQ-AAT

32GB

LBGA

System.Object[]

5

-40C to +105C

100-ball

14 x 18 x 1.4

Automotive

x8

MTFC32GAKAEEF-AAT

32GB

TFBGA

System.Object[]

5

-40C to +105C

169-ball

14 x 18 x 1.2

Automotive

x8

MTFC32GAPALBH-IT

32GB

TFBGA

3.3V

5.1

-40C to +85C

153-ball

11.5 x 13 x 1.1

(Empty)

x8

MTFC32GAPALGT-AAT

32GB

WFBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

13x11.5x0.8

Automotive

x8

MTFC32GAPALGT-AIT

32GB

WFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x0.8

Automotive

x8

MTFC32GAPALHT-AIT

32GB

VBGA

2.7V-3.6V

5.1

-40C to +85C

100-ball

18x14x1

Automotive

x8

MTFC32GAPALNA-AAT

32GB

TBGA

2.7V-3.6V

5.1

-40C to +105C

100-ball

18x14x1.2

Automotive

x8

MTFC32GAPALNA-AIT

32GB

TBGA

2.7V-3.6V

5.1

-40C to +85C

100-ball

18x14x1.2

Automotive

x8

MTFC32GAZAQDW-AAT

32GB

LBGA

2.7V-3.6V

5.1

-40C to +105C

(Empty)

(Empty)

Automotive

x8

MTFC32GAZAQHD-AAT

32GB

VFBGA

2.7V-3.6V

5.1

-40C to +105C

(Empty)

(Empty)

Automotive

x8

MTFC32GAZAQHD-AIT

32GB

VFBGA

2.7V-3.6V

5.1

-40C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC32GAZAQHD-IT

32GB

VFBGA

2.7V-3.6V

5.1

-40C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC32GAZAQHD-WT

32GB

VFBGA

2.7V-3.6V

5.1

-25C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC4GLGDQ-AIT A

32GB

LBGA

3.3V

4.41

-40C to +85C

100-ball

14 x 18 x 1.4

Automotive

x8

MTFC4GLWDM-4M AAT A

32GB

TFBGA

3.3V

4.51

-40C to +105C

153-ball

(Empty)

Automotive

x8

MTFC64GAPALGT-AAT

64GB

WFBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

13x11.5x0.8

Automotive

x8

MTFC64GAPALGT-AIT

64GB

WFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x0.8

Automotive

x8

MTFC64GAPALHT-AIT

64GB

VBGA

2.7V-3.6V

5.1

-40C to +85C

100-ball

18x14x1

Automotive

x8

MTFC64GAPALNA-AAT

64GB

TBGA

2.7V-3.6V

5.1

-40C to +105C

100-ball

18x14x1.2

Automotive

x8

MTFC64GAXAQEA-WT

512GB

WFBGA

3.3V

5.1

-25C to +85C

(Empty)

(Empty)

(Empty)

x8

MTFC64GAZAQHD-AAT

64GB

VFBGA

2.7V-3.6V

5.1

-40C to +105C

(Empty)

(Empty)

Automotive

x8

MTFC64GAZAQHD-AIT

64GB

VFBGA

2.7V-3.6V

5.1

-40C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC64GAZAQHD-IT

64GB

VFBGA

2.7V-3.6V

5.1

-40C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC64GAZAQHD-WT

64GB

VFBGA

2.7V-3.6V

5.1

-25C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC8GACAEDQ-AAT

8GB

LBGA

System.Object[]

5

-40C to +105C

100-ball

14 x 18 x 1.4

Automotive

x8

MTFC8GACAENS-AAT

8GB

TFBGA

System.Object[]

5

-40C to +105C

153-ball

11.5 x 13 x 1.2

Automotive

x8

MTFC8GAMALBH-AAT

8GB

TFBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

13x11.5x1.1

Automotive

x8

MTFC8GAMALBH-AIT

8GB

TFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x1.1

Automotive

x8

MTFC8GAMALBH-IT

8GB

TFBGA

3.3V

5.1

-40C to +85C

153-ball

(Empty)

Automotive

x8

MTFC8GAMALGT-AAT

8GB

WFBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

13x11.5x0.8

Automotive

x8

MTFC8GAMALGT-AIT

8GB

WFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x0.8

Automotive

x8

MTFC8GAMALHT-AAT

8GB

VBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

18x14x1

Automotive

x8

MTFC8GAMALHT-AIT

8GB

VBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

18x14x1

Automotive

x8

MTFC8GAMALNA-AAT

8GB

TBGA

2.7V-3.6V

5.1

-40C to +105C

100-ball

18x14x1.2

Automotive

x8

MTFC8GAMALNA-AIT

8GB

TBGA

2.7V-3.6V

5.1

-40C to +85C

100-ball

18x14x1.2

Automotive

x8

MTFC128GAPALBH-AIT

128GB

WFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x1.1

Automotive

x8

MTFC128GAPALNS-AAT

128GB

TFBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

13x11.5x1.2

Automotive

x8

MTFC128GAPALNS-AIT

128GB

TFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x1.2

Automotive

x8

MTFC128GAZAQJP-AAT

128GB

VFBGA

2.7V-3.6V

5.1

-40C to +105C

(Empty)

(Empty)

Automotive

x8

MTFC128GAZAQJP-AIT

128GB

VFBGA

2.7V-3.6V

5.1

-40C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC128GAZAQJP-IT

128GB

VFBGA

2.7V-3.6V

5.1

-40C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC16GAKAEDQ-AAT

16GB

LBGA

System.Object[]

5

-40C to +105C

100-ball

14 x 18 x 1.4

Automotive

x8

MTFC16GAKAEEF-AAT

16GB

TFBGA

System.Object[]

5

-40C to +105C

169-ball

14 x 18 x 1.2

Automotive

x8

MTFC16GAPALBH-AAT

16GB

TFBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

13x11.5x1.1

Automotive

x8

MTFC16GAPALBH-AIT

16GB

TFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x1.1

Automotive

x8

MTFC16GAPALGT-AAT

16GB

WFBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

13x11.5x0.8

Automotive

x8

MTFC16GAPALGT-AIT

16GB

WFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x0.8

Automotive

x8

MTFC16GAPALNA-AAT

16GB

TBGA

2.7V-3.6V

5.1

-40C to +105C

100-ball

18x14x1.2

Automotive

x8

MTFC16GAPALNA-AIT

16GB

TBGA

2.7V-3.6V

5.1

-40C to +85C

100-ball

18x14x1.2

Automotive

x8

MTFC32GAKAEDQ-AAT

32GB

LBGA

System.Object[]

5

-40C to +105C

100-ball

14 x 18 x 1.4

Automotive

x8

MTFC32GAKAEEF-AAT

32GB

TFBGA

System.Object[]

5

-40C to +105C

169-ball

14 x 18 x 1.2

Automotive

x8

MTFC32GAPALGT-AAT

32GB

WFBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

13x11.5x0.8

Automotive

x8

MTFC32GAPALGT-AIT

32GB

WFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x0.8

Automotive

x8

MTFC32GAPALHT-AIT

32GB

VBGA

2.7V-3.6V

5.1

-40C to +85C

100-ball

18x14x1

Automotive

x8

MTFC32GAPALNA-AAT

32GB

TBGA

2.7V-3.6V

5.1

-40C to +105C

100-ball

18x14x1.2

Automotive

x8

MTFC32GAPALNA-AIT

32GB

TBGA

2.7V-3.6V

5.1

-40C to +85C

100-ball

18x14x1.2

Automotive

x8

MTFC32GAZAQDW-AAT

32GB

LBGA

2.7V-3.6V

5.1

-40C to +105C

(Empty)

(Empty)

Automotive

x8

MTFC32GAZAQHD-AAT

32GB

VFBGA

2.7V-3.6V

5.1

-40C to +105C

(Empty)

(Empty)

Automotive

x8

MTFC32GAZAQHD-AIT

32GB

VFBGA

2.7V-3.6V

5.1

-40C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC32GAZAQHD-IT

32GB

VFBGA

2.7V-3.6V

5.1

-40C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC32GAZAQHD-WT

32GB

VFBGA

2.7V-3.6V

5.1

-25C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC4GLGDQ-AIT A

32GB

LBGA

3.3V

4.41

-40C to +85C

100-ball

14 x 18 x 1.4

Automotive

x8

MTFC4GLWDM-4M AAT A

32GB

TFBGA

3.3V

4.51

-40C to +105C

153-ball

(Empty)

Automotive

x8

MTFC64GAPALGT-AAT

64GB

WFBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

13x11.5x0.8

Automotive

x8

MTFC64GAPALGT-AIT

64GB

WFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x0.8

Automotive

x8

MTFC64GAPALHT-AIT

64GB

VBGA

2.7V-3.6V

5.1

-40C to +85C

100-ball

18x14x1

Automotive

x8

MTFC64GAPALNA-AAT

64GB

TBGA

2.7V-3.6V

5.1

-40C to +105C

100-ball

18x14x1.2

Automotive

x8

MTFC64GAZAQHD-AAT

64GB

VFBGA

2.7V-3.6V

5.1

-40C to +105C

(Empty)

(Empty)

Automotive

x8

MTFC64GAZAQHD-AIT

64GB

VFBGA

2.7V-3.6V

5.1

-40C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC64GAZAQHD-IT

64GB

VFBGA

2.7V-3.6V

5.1

-40C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC64GAZAQHD-WT

64GB

VFBGA

2.7V-3.6V

5.1

-25C to +85C

(Empty)

(Empty)

Automotive

x8

MTFC8GACAEDQ-AAT

8GB

LBGA

System.Object[]

5

-40C to +105C

100-ball

14 x 18 x 1.4

Automotive

x8

MTFC8GACAENS-AAT

8GB

TFBGA

System.Object[]

5

-40C to +105C

153-ball

11.5 x 13 x 1.2

Automotive

x8

MTFC8GAMALBH-AAT

8GB

TFBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

13x11.5x1.1

Automotive

x8

MTFC8GAMALBH-AIT

8GB

TFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x1.1

Automotive

x8

MTFC8GAMALBH-IT

8GB

TFBGA

3.3V

5.1

-40C to +85C

153-ball

(Empty)

Automotive

x8

MTFC8GAMALGT-AAT

8GB

WFBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

13x11.5x0.8

Automotive

x8

MTFC8GAMALGT-AIT

8GB

WFBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

13x11.5x0.8

Automotive

x8

MTFC8GAMALHT-AAT

8GB

VBGA

2.7V-3.6V

5.1

-40C to +105C

153-ball

18x14x1

Automotive

x8

MTFC8GAMALHT-AIT

8GB

VBGA

2.7V-3.6V

5.1

-40C to +85C

153-ball

18x14x1

Automotive

x8

MTFC8GAMALNA-AAT

8GB

TBGA

2.7V-3.6V

5.1

-40C to +105C

100-ball

18x14x1.2

Automotive

x8

MTFC8GAMALNA-AIT

8GB

TBGA

2.7V-3.6V

5.1

-40C to +85C

100-ball

18x14x1.2

Automotive

x8

MCP

MT29AZ5A3CHHWD-18AAT

4Gb

(Empty)

LPDDR2

2Gb

x8

x32

1.8V

VFBGA

162-ball

MT29AZ5A3CHHWD-18AIT

4Gb

(Empty)

LPDDR2

2Gb

x8

x32

1.8V

VFBGA

162-ball

MT29C1G12MAAJVAMD-5 IT

1Gb

(Empty)

LPDDR

512Mb

x8

x16

1.7V-1.9V

VFBGA

130-ball

MT29C2G24MAAAAKAKD-5 IT

2Gb

(Empty)

LPDDR

1Gb

x8

x32

1.7V-1.9V

TFBGA

137-ball

MT29C2G24MAAAAKAMD-5 IT

2Gb

(Empty)

LPDDR

1Gb

x8

x32

1.7V-1.9V

VFBGA

130-ball

MT29C2G24MAABAHAMD-5 IT

2Gb

(Empty)

LPDDR

1Gb

x16

x16

1.7V-1.9V

VFBGA

130-ball

MT29C4G48MAAGBBAKS-48 IT

4Gb

(Empty)

LPDDR

2Gb

x8

x32

1.7V-1.9V

VFBGA

137-ball

MT29C4G48MAYBBAKS-48 IT

4Gb

(Empty)

LPDDR

2Gb

x8

x16

1.7V-1.9V

VFBGA

137-ball

MT29C4G48MAYBBAMR-48 IT

4Gb

(Empty)

LPDDR

2Gb

x8

x32

1.7V-1.9V

VFBGA

130-ball

MT29C4G48MAZBBAKB-48 IT

4Gb

(Empty)

LPDDR

2Gb

x16

x16

1.7V-1.9V

WFBGA

168-ball

MT29C4G48MAZBBAKS-48 IT

4Gb

(Empty)

LPDDR

2Gb

x16

x32

1.7V-1.9V

VFBGA

137-ball

MT29GZ5A3BPGGA-046IT

4Gb

(Empty)

(Empty)

2Gb

x16

(Empty)

(Empty)

VFBGA

(Empty)

MT29GZ5A3BPGGA-53IT

4Gb

(Empty)

(Empty)

(Empty)

(Empty)

(Empty)

(Empty)

(Empty)

(Empty)

MT29GZ5A5BPGGA-046AAT

4Gb

(Empty)

(Empty)

(Empty)

x16

x32

1.8V

WFBGA

(Empty)

MT29GZ5A5BPGGA-046AIT

4Gb

(Empty)

(Empty)

(Empty)

x16

x32

1.8V

WFBGA

(Empty)

MT29GZ5A5BPGGA-046IT

4Gb

(Empty)

(Empty)

(Empty)

x16

x32

1.8V

WFBGA

(Empty)

MT29GZ5A5BPGGA-53AAT

4Gb

(Empty)

LPDDR4

4Gb

x8

x32

1.8V

WFBGA

149-ball

MT29GZ5A5BPGGA-53AIT

4Gb

(Empty)

(Empty)

(Empty)

x8

x32

1.8V

(Empty)

(Empty)

MT29GZ5A5BPGGA-53IT

4Gb

(Empty)

LPDDR4

4Gb

x8

x32

1.8V

WFBGA

149-ball

MT29GZ6A6BPIET-046AAT

8Gb

(Empty)

(Empty)

8Gb

x16

(Empty)

(Empty)

VFBGA

(Empty)

MT29GZ6A6BPIET-046AIT

8Gb

(Empty)

(Empty)

8Gb

x16

(Empty)

(Empty)

VFBGA

(Empty)

MT29GZ6A6BPIET-046IT

8Gb

(Empty)

(Empty)

8Gb

x16

(Empty)

(Empty)

VFBGA

(Empty)

MT29GZ6A6BPIET-53AAT

8Gb

(Empty)

(Empty)

8Gb

x16

(Empty)

(Empty)

VFBGA

(Empty)

MT29GZ6A6BPIET-53AAT

8Gb

(Empty)

(Empty)

8Gb

x16

(Empty)

(Empty)

VFBGA

(Empty)

MT29GZ6A6BPIET-53AIT

8Gb

(Empty)

(Empty)

8Gb

x16

(Empty)

(Empty)

VFBGA

(Empty)

MT29GZ6A6BPIET-53IT

8Gb

(Empty)

(Empty)

8Gb

x16

(Empty)

(Empty)

VFBGA

(Empty)

MT29RZ1C1CZZHGTN-18I

1Gb

(Empty)

LPDDR2

512Mb

x8

x16

1.8V

WFBGA

121-ball

MT29RZ1CVCZZHGTN-18 I

1Gb

(Empty)

LPDDR2

512Mb

x16

x16

1.8V

WFBGA

121-ball

MT29RZ4B2DZZHHTB-18I

4Gb

(Empty)

LPDDR2

2Gb

x32

x32

1.8V

VFBGA

162-ball

MT29RZ4B2DZZHHTB-18W

4Gb

(Empty)

LPDDR2

2Gb

x32

x32

1.8V

VFBGA

162-ball

MT29RZ4B2DZZHHWD-18I

4Gb

(Empty)

LPDDR2

2Gb

x32

x32

1.8V

VFBGA

162-ball

MT29RZ4B4DZZMGWD-18I

4Gb

(Empty)

LPDDR2

4Gb

x8

x32

1.8V

VFBGA

162-ball

MT29V5D7GVESL-046I

256GB

(Empty)

(Empty)

16Gb

x32

(Empty)

(Empty)

VFBGA

(Empty)

MT29VZZZ5D8JQFSL-053

64Gb

(Empty)

(Empty)

(Empty)

x32

x16

(Empty)

VFBGA

254-ball

MT29VZZZ7D8FQFSL-046 W

64GB

UFS 2.1

LPDDR4x

24Gb

x32

x32

1.8V

VFBGA

254-ball

MT29VZZZ7D8GUFSL-046

536Gb

(Empty)

(Empty)

(Empty)

x16

x16

(Empty)

(Empty)

(Empty)

MT29VZZZAD81SFSL-046

64GB

UFS 2.2

LPDDR4x

32Gb

x32

x16

(Empty)

(Empty)

(Empty)

MT29VZZZAD8FQFSL-046 W

64GB

UFS 2.1

LPDDR4x

32Gb

x32

x32

1.8V

VFBGA

254-ball

MT29VZZZAD8GQFSL-046

256Gb

(Empty)

(Empty)

32Gb

x32

x16

(Empty)

(Empty)

254-ball

MT29VZZZAD8GUFSL-046

544Gb

(Empty)

(Empty)

(Empty)

x16

x16

(Empty)

(Empty)

(Empty)

MT29VZZZAD9FQFSM-046 W

128GB

UFS 2.1

LPDDR4x

32Gb

x32

x32

(Empty)

VFBGA

254-ball

MT29VZZZAD9GQFSM-046

256Gb

(Empty)

(Empty)

32Gb

x32

x16

(Empty)

VFBGA

254-ball

MT29VZZZBD8FQKSM-046 W

64GB

UFS 2.1

LPDDR4x

48Gb

x32

x32

1.8V

VFBGA

254-ball

MT29VZZZBD91SLSM-046

128GB

UFS 2.2

LPDDR4x

48Gb

x16,x32

x16

(Empty)

(Empty)

(Empty)

MT29VZZZBD9FQKPR-046 W

128GB

UFS 2.1

LPDDR4x

48Gb

x32

x32

1.8V

TFBGA

254-ball

MT29VZZZBDA1SLPR-046

256GB

UFS 2.2

LPDDR4x

48Gb

x16,x32

x16

(Empty)

(Empty)

(Empty)

MT29VZZZBDAFQKBA-046 W

256GB

UFS 2.1

LPDDR4x

48Gb

x32

x32

1.8V

TFBGA

254-ball

MT29VZZZBDAFQKWL-046 W

256GB

UFS 2.1

LPDDR4x

48Gb

x32

x32

1.8V

TFBGA

254-ball

MT29VZZZCD91SFSM-046

128GB

UFS 2.2

LPDDR4x

32Gb

x32

x16

(Empty)

(Empty)

(Empty)

MT29VZZZCD91SKSM-046

128GB

UFS 2.2

LPDDR4x

64Gb

x16

x16

(Empty)

(Empty)

(Empty)

MT29VZZZCD9FQKPR-046 W

128GB

UFS 2.1

LPDDR4x

64Gb

x32

x32

1.8V

TFBGA

254-ball

MT29VZZZCD9GQKPR-046

256Gb

(Empty)

(Empty)

64Gb

x16

x16

(Empty)

TFBGA

(Empty)

MT29VZZZCDA1SKPR-046

256GB

UFS 2.2

LPDDR4x

64Gb

x16

x16

(Empty)

(Empty)

(Empty)

MT29VZZZCDAFQKBA-046 W

256GB

UFS 2.1

LPDDR4x

64Gb

x32

x32

1.8V

TFBGA

254-ball

MT29VZZZCDAFQKWL-046 W

256GB

UFS 2.1

LPDDR4x

64Gb

x32

x32

1.8V

TFBGA

254-ball

MT30AZZZCD9ZTOQS-031 W

128GB

UFS 3.1

LPDDR5

64Gb

x32

x32

1.8V

TFBGA

297-ball

MT30AZZZCDAZTOWL-031 W

256GB

UFS 3.1

LPDDR5

64Gb

x32

x32

1.8V

TFBGA

297-ball

MT30AZZZDD9ZTPWL-031 W

128GB

UFS 3.1

LPDDR5

96Gb

x32

x32

1.8V

TFBGA

297-ball

MT30AZZZDDAZTPEQ-031 W

256GB

UFS 3.1

LPDDR5

96Gb

x32

x32

1.8V

LFBGA

297-ball

3D NAND

MT29F128G08CBCEBJ4-37ITR

128Gb

Mass Storage

MLC

(Empty)

-40C to +85C

3.3V

VBGA

132-ball

533 MT/s

MT29F16T08EWLCHD6-T

16Tb

3D NAND

TLC

FortisMax

0C to +70C

(Empty)

LFBGA

(Empty)

(Empty)

MT29F1T08EBLCHD4-R

1Tb

3D NAND

TLC

FortisFlash

0C to +70C

2.5V

VFBGA

(Empty)

(Empty)

MT29F1T08EBLCHD4-T

1Tb

3D NAND

TLC

FortisMax

0C to +70C

(Empty)

VFBGA

(Empty)

(Empty)

MT29F1T08EEHAFJ4-3R

1Tb

3D NAND

TLC

FortisFlash

0C to +70C

3.3V

VBGA

132-ball

667 MT/s

MT29F1T08EEHAFJ4-3T

1Tb

3D NAND

TLC

FortisMax

0C to +70C

3.3V

VBGA

132-ball

667 MT/s

MT29F1T08EEHBFJ4-R

1Tb

3D NAND

TLC

FortisFlash

0C to +70C

3.3V

VBGA

132-ball

800 MT/s

MT29F1T08EEHBFJ4-T

1Tb

3D NAND

TLC

FortisMax

0C to +70C

3.3V

VBGA

132-ball

800 MT/s

MT29F1T08EELCEJ4-R

1Tb

3D NAND

TLC

FortisFlash

0C to +70C

2.5V

VBGA

132-ball

1200 MT/s

MT29F1T08EELEEJ4-R

1Tb

3D NAND

TLC

FortisFlash

0C to +70C

2.5V

VBGA

(Empty)

(Empty)

MT29F1T08EELEEJ4-T

1Tb

3D NAND

TLC

FortisMax

0C to +70C

2.5V

VBGA

(Empty)

(Empty)

MT29F1T08EMHAFJ4-3R

1Tb

3D NAND

TLC

FortisFlash

0C to +70C

3.3V

VBGA

132-ball

667 MT/s

MT29F256G08CECEBJ4-37ITR

256Gb

Mass Storage

SLC

(Empty)

-40C to +85C

3.3V

VBGA

132-ball

533 MT/s

MT29F256G08EBCAGB16A3WC1

256Gb

3D NAND

TLC

(Empty)

0C to +70C

3.3V

Wafer

(Empty)

(Empty)

MT29F256G08EBHAFJ4-3R

256Gb

3D NAND

TLC

FortisFlash

0C to +70C

3.3V

VBGA

132-ball

667 MT/s

MT29F2T08EELCHD4-R

2Tb

3D NAND

TLC

FortisFlash

0C to +70C

(Empty)

(Empty)

(Empty)

(Empty)

MT29F2T08EELCHD4-T

2Tb

3D NAND

TLC

FortisMax

0C to +70C

(Empty)

VFBGA

(Empty)

(Empty)

MT29F2T08EMHAFJ4-3R

2Tb

3D NAND

TLC

FortisFlash

0C to +70C

3.3V

VBGA

132-ball

667 MT/s

MT29F2T08EMHAFJ4-3T

2Tb

3D NAND

TLC

FortisMax

0C to +70C

3.3V

VBGA

132-ball

667 MT/s

MT29F2T08EMHBFJ4-R

2Tb

3D NAND

TLC

FortisFlash

0C to +70C

3.3V

VBGA

132-ball

800 MT/s

MT29F2T08EMHBFJ4-T

2Tb

3D NAND

TLC

FortisMax

0C to +70C

3.3V

VBGA

132-ball

800 MT/s

MT29F2T08EMLCEJ4-R

2Tb

3D NAND

TLC

FortisFlash

0C to +70C

2.5V

VBGA

132-ball

1200 MT/s

MT29F2T08EMLEEJ4-R

2Tb

3D NAND

TLC

FortisFlash

0C to +70C

2.5V

VBGA

(Empty)

(Empty)

MT29F2T08EMLEEJ4-T

2Tb

3D NAND

TLC

FortisMax

0C to +70C

2.5V

VBGA

(Empty)

(Empty)

MT29F4T08EMLCHD4-R

4Tb

3D NAND

TLC

FortisFlash

0C to +70C

2.5V

VFBGA

(Empty)

(Empty)

MT29F4T08EMLCHD4-T

4Tb

3D NAND

TLC

FortisMax

0C to +70C

(Empty)

VFBGA

(Empty)

(Empty)

MT29F4T08EUHAFM4-3R

4Tb

3D NAND

TLC

FortisFlash

0C to +70C

3.3V

LBGA

132-ball

667 MT/s

MT29F4T08EUHAFM4-3T

4Tb

3D NAND

TLC

FortisMax

0C to +70C

3.3V

LBGA

132-ball

667 MT/s

MT29F4T08EUHBFM4-R

4Tb

3D NAND

TLC

FortisFlash

0C to +70C

3.3V

LBGA

132-ball

800 MT/s

MT29F4T08EUHBFM4-T

4Tb

3D NAND

TLC

FortisMax

0C to +70C

3.3V

LBGA

132-ball

800 MT/s

MT29F4T08EULCEM4-R

4Tb

3D NAND

TLC

FortisFlash

0C to +70C

2.5V

LBGA

132-ball

1200 MT/s